Verilog generate statement is a powerful construct for writing configurable, synthesizable RTL It can be used to create multiple instantiations of modules and code, or conditionally instantiate blocks of code However, many Verilog programmers often have questions about how to use Verilog generate effectively Using set_parameter for Quartus compile directives in VHDL and Verilog Description This forum article is dedicated to help users apply the the set_parameter qsf assignment in order to enable or disable certain portions of their RTL codeAlways @(posedge clk) begin `ifdef (param == 0) // < counter

Verilog For Computer Design Ppt Download

Verilog ifdef parameter

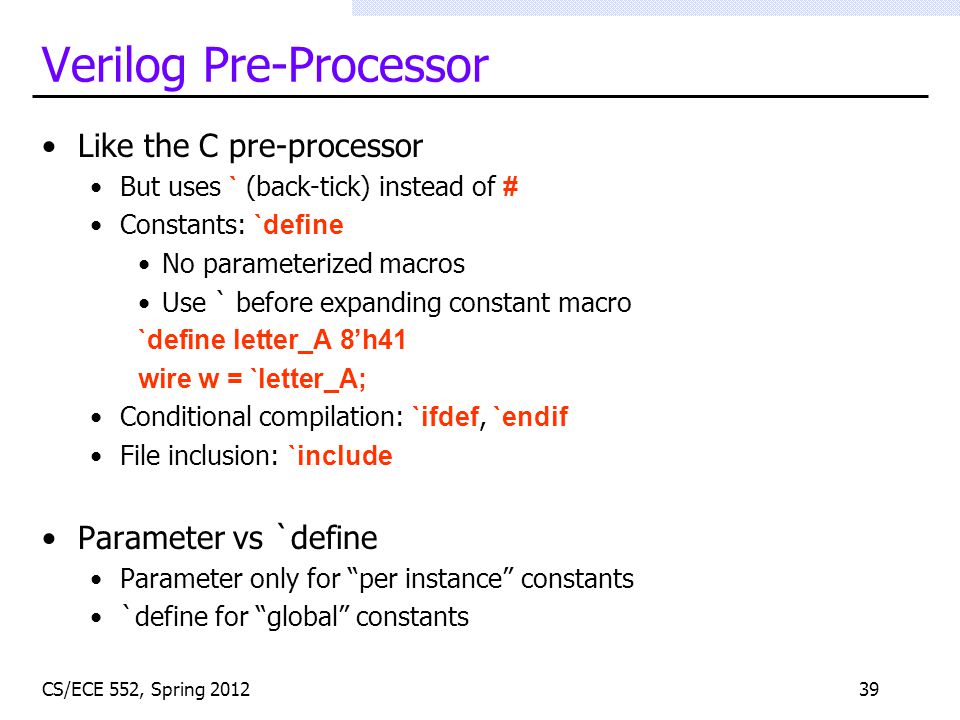

Verilog ifdef parameter-Checks that a Verilog `endif directive is followed by a comment that matches the name of the opening `ifdef or `ifndef See Style endifcommentVerilog Compiler Directives macro_code // parameterized macro `undef macro_name // undefine a macro `ifdef macro_name1 // include source lines1 if macro_name1 is defined // the source lines1 `elsif macro_name2 // any number of elsif clauses, the first defined // macro_name includes the source lines `else

Verilog Archives Verification Guide

Parametrised Verilog Counter GitHub Gist instantly share code, notes, and snippets A `define is a global macro It is of global scope If you define in a module, it still stays declared after the module After it is defined, is referenced using the macro name with a preceding ` (backtic) character It can exist either inside or outside of a module declaration, and both are treated the sameThis page contains Verilog tutorial, Verilog Syntax, Verilog Quick Reference, PLI, modelling memory and FSM, Writing Testbenches in Verilog, Lot of Verilog Examples and Verilog in One Day Tutorial `ifdef Optionally includes lines of source code during compilation The `ifdef directive checks that a macro has been defined, and if so

`ifdef c_input input c; Thus, any code written inside `ifdef and `endif directive will be compiled only when a particular macro is defined Syntax `ifdef macro_name `endif The macros can either be defined using `define directive or be passed as a parameterA macro can be defined with arguments, so every macro call can be followed by actual parameters The compiler recognizes a macro by its name preceded by accent grave (`) character `ifdef, `else, and `endif These directives can be used to decide which lines of Verilog code should be included for the compilation (Example 4)

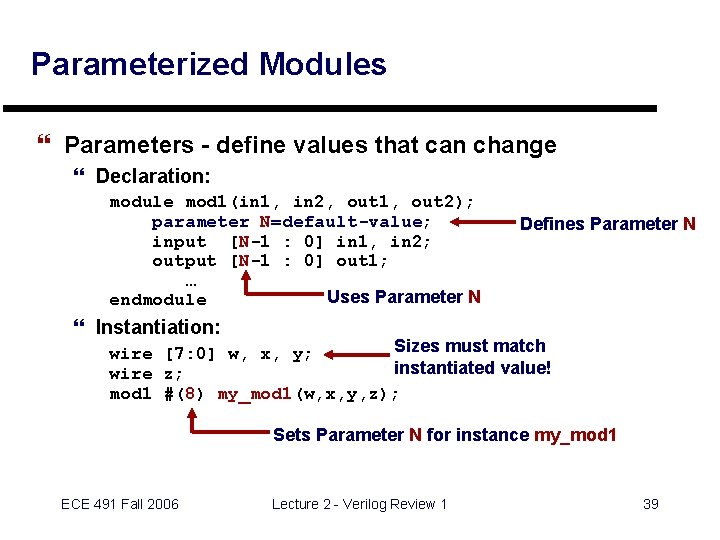

The veribleverilogsyntax doesn't generate preprocessor token correctly on parameter list with ANSI style module header Test case // examplesv module example # ( `ifdef PP_ID parameter bits = 12 `else parameter bits = 24 `endif ); The defined parameter value can be changed in two ways module instantiation and defparam statement In each module instance, we can override the parameter values at compile time we can override the single parameter value or multiple parameter values also The Eda playground example for single parameters override in Verilog STYLE_NO 1Create and add the Verilog module, named add_two_values_task, that defines a task called add_two_values The task will take two 4bit parameters, add them, and output a 4bit sum and a carry The module will call the task with the operands

Ece 491 Senior Design I Lecture 2 Verilog

Understanding Linear Implementation Of A Round Robin Arbiter

Verilog has following conditional compiler directives The `ifdef compiler directive checks for the definition of a text_macro_name If the text_macro_name is defined, then the lines following the `ifdef directive are included If the text_macro_name is not defined and an `else directive exists, then this source is compiled One can use `ifdef `endif to check whether the macro is defined or not Moreover, one can use an optional generate block to test the value of macro/parameters Moreover, one can use an optional generate block to test the value of macro/parametersAnother enhancement in Verilog 01 is the addition of localparam With localparam, you do not allow it to be changed directly with instantiation However, localparam can be expressed in terms of parameter and when the value of the parameter changes on intantiation, the localparam changes

Verilog Interview Questions Answers

System Verilog Macro A Powerful Feature For Design Verification Projects

Conditional compilation can be achieved with Verilog `ifdef and `ifndef keywords These keywords can appear anywhere in the design and can be nested one inside the other The keyword `ifdef simply tells the compiler to include the piece of code until the next `else or `endif if the given macro called FLAG is defined using a `define directiveConditional Compilation (#if, #ifdef, #ifndef, #else, #elif,

0 件のコメント:

コメントを投稿